集成电路应用与设计研究室(ICAD1)

ICAD1:Integrated Circuit Application & Design Lab 1

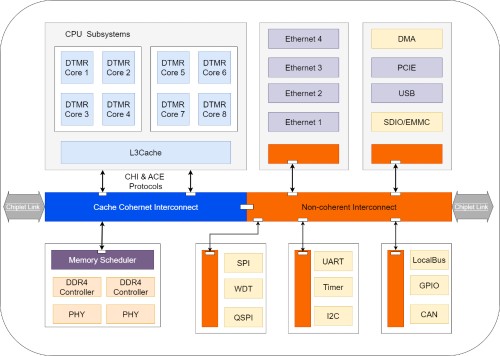

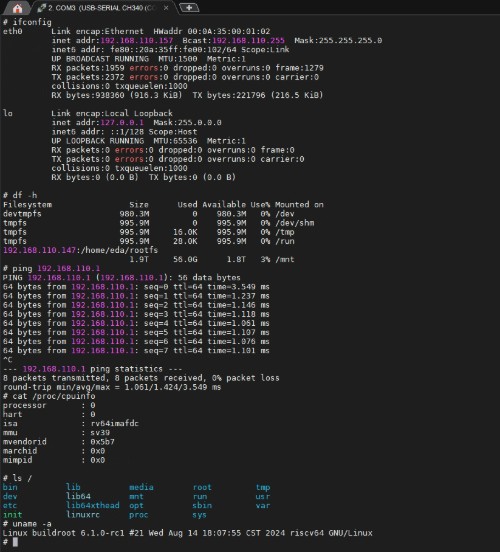

1. 研发成功RISC-V 64核服务器CPU

-

12nm先进工艺

-

最多可以支持2个物理CPU

Up to 2 socket CPUs

-

64个RSIC-V内核

64cores base on RISC-V ISA

-

每个物理CPU最高配置4个DIMM内存(RDIMM &UDIMM),最高每个物理CPU可以支持256GB内存容量

Each physical CPU can be configured with maximum 4 DIMMs (RDIMM & UDIMM), with the maximum memory capacity up to 256GB

-

最大32条PCIe 4.0通道

Each CPU up to 32 PCIe 4.0 lanes

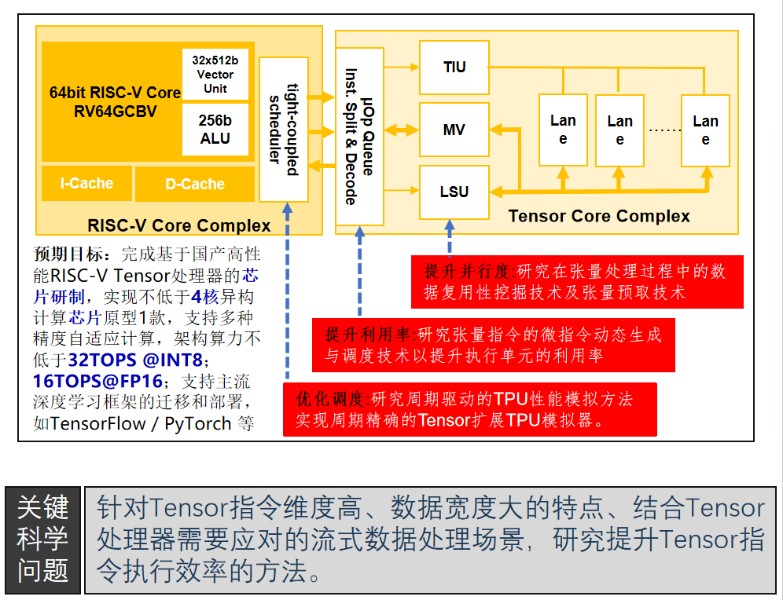

2. 基于RISC-V Tensor指令集扩展的TPU

针对基于RISC-V人工智能(AI)指令集扩展的智能处理器中的Tensor执行效率低、存储墙瓶颈和系统软件难兼顾多样化AI芯片的问题

研究面向RISC-V 张量指令扩展的处理器架构

研究面向RISC-V TPU的近存计算架构设计

研究统一的编程模型、编译器和系统软件栈,构建完整的软硬件协同优化技术体系和工具集

实现计算资源利用效率和软件调优能力的提升,并在开源处理器核和不少于10种AI模型上验证

3. 研发成功BM1684XTPU

12nm先进工艺

高性能低功耗8核CA53,2.3GHz

内存16GB LPDDR4x 128bit 68.256GB/s

支持FP32和INT8等多种精度自适应计算

支持32TOPS INT8算力 支持16TFlops的FP16/BF16算力

支持2TFlops的FP32算力

支持各种主流深度学习框架的迁移和部署

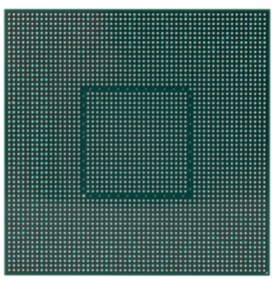

4. 研发高可靠、高性能RISC-V 处理器芯片

单核对标飞腾D2000芯片

基于RISC-V指令集CPU核心,64位,单核CoreMark性能

>5.0CoreMarks/MHz

10级以上流水线架构,深度乱序执行,动态分支预测

支持AXI、APB、AHB等总线协议

多核架构,多级cache最大32条PCIe 4.0通道

支持FreeRTOS和Linux

支持C,C++,Java,Python 3.10,Go语言

一位反转免疫,检测两位反转并采取措施

支持docker,支持4个千兆网口

功耗<20W ,约1亿门电路规模

支持PCIe,USB,DDR,Ethernet,SD,CAN等外设

5. 研发FPGA验证平台

Xilinx Virtex UltraScale XCVU440FLGA2892C

满足 2600 万 ASIC 门的设计验证

5540K 系统逻辑单元

88.6Mb Block RAM

2880 DSP

在FPGA原型验证平台上的SOC设计中运行Linux

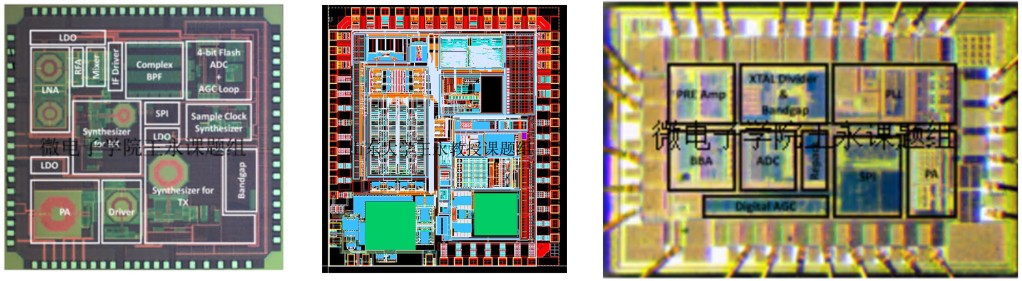

6. 射频前端及传感模块

优于国家北斗系统的入网标准,达到国内先进水平,已通过中国电子科技集团实现产业化。

7. 高性能北斗导航芯片

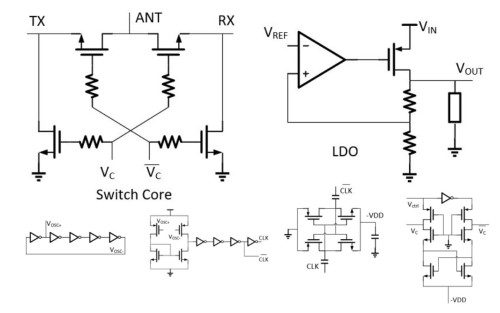

基于SOI-CMOS工艺的射频前端模块研究:

1. 低插损高隔离度的射频开关及偏置电路

2. 高输出电压精度的低压差线性稳压器

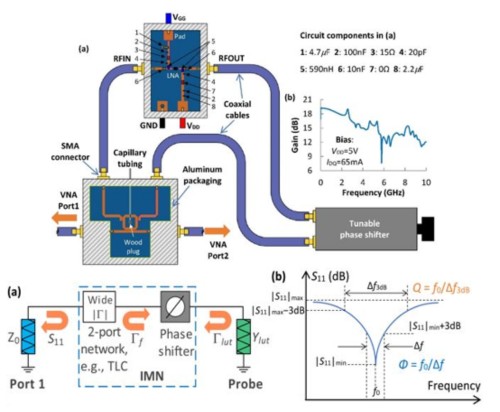

射频传感技术:

1. 基于有源反馈电路的高品质因数射频检测器

2. 基于可调阻抗匹配网络的同轴探针谐振式测量

代表论文:

“A Tunable High-Q Microwave Detector for On-Column Capillary Liquid Chromatography,”IEEE Trans. Instrum. Meas., 2020.

“Slow microwave sensor based on engineered -1/x-like function transmission for improved sensitivity,”IEEE Trans. Instrum. Meas., 2021.

“Microwave Measurement of Bovine Serum Albumin Solutions Based on High-Q/High-Resolution Resonator,”IEEE Trans. Microw. Theory Techn., 2022.

“Resonant Measurement of Coaxial Probe Based on Tunable Impedance Matching Network,”IEEE Microw. Wireless Technol. Lett., 2023.

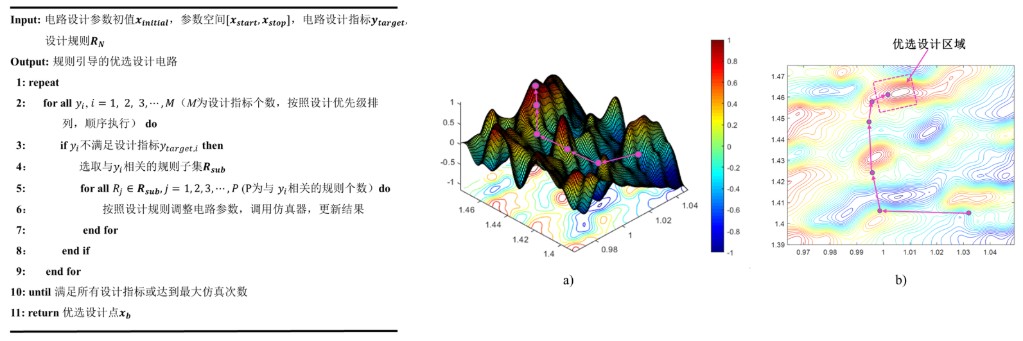

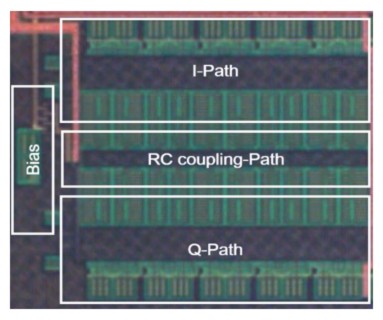

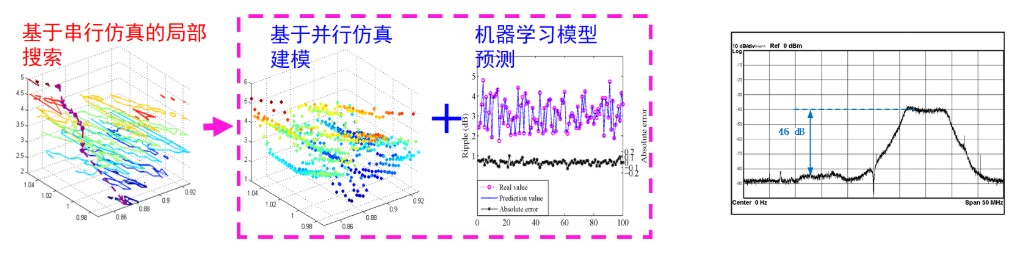

8. 模拟集成电路参数优化

机器学习+优化算法:方便快捷

规则驱动:为设计工程师一个开放式的优化系统,让设计工程师“驾驶”优化引擎

基于遗传算法的模拟电路参数优化软件在联暻半导体的实际设计中得到了应用。

-

复数带通滤波器的研究与设计

-

模拟集成电路自动优化方法研究

-

机器学习模型代替SPICE仿真,实现更快评估

-

并行仿真产生训练数据,不再需要串行仿真

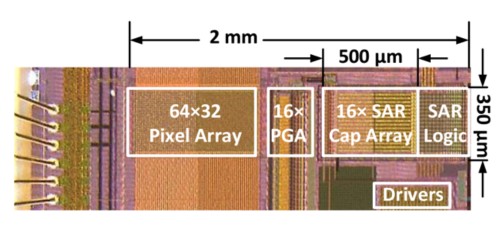

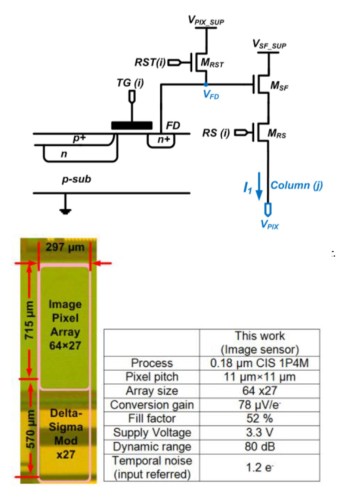

9. 图像传感器芯片

Above Figure: Micrograph of the chip, with each block (pixel array, SAR ADC, capacitor array, etc.) labelled, with its dimensions.

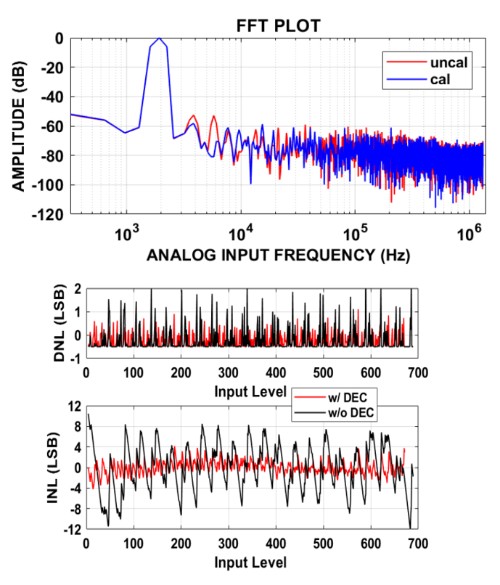

Right above Figure: Measured FFT spectral response of column #8 at a -3 dB 3.66 kHz sine wave input, and a conversion frequency of 5 MHz, without (red) and with (blue) digital background calibration.

Right bottom Figure: Measured FFT spectral response of column #8 at a -3 dB 3.66 kHz sine wave input, and a conversion frequency of 5 MHz, without (red) and with (blue) digital background calibration.

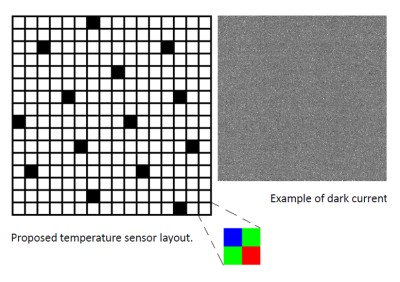

10. 图像传感器芯片

利用图像传感器像素本身进行温度感应

用Incremental Delta-sigma ADC作为列读出电路,让噪声降低到符合温度传感器要求的程度

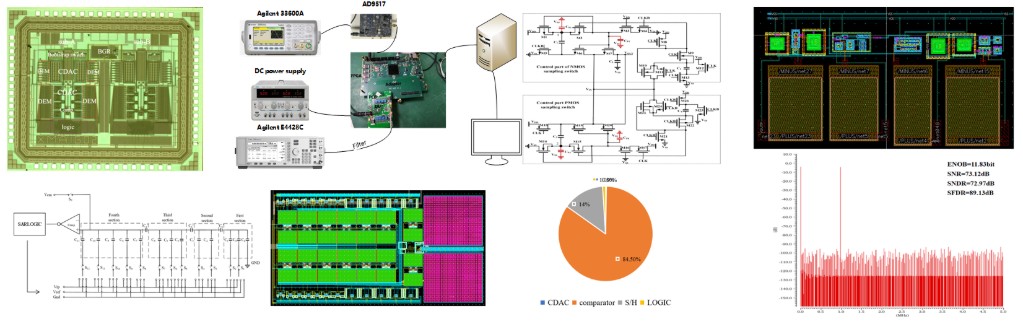

11. 高性能模数转换器芯片

高精度SAR ADC SMIC CMOS 180nm

DEM技术和Split ADC等校准技术

自举开关、电容阵列等关键电路模块优化……