为帮助本院学生了解类脑器件与存算一体芯片的相关知识,3月31日晚,集成电路学院举办了“芯”系未来系列活动(第六十期)——柔性低功耗神经形态类脑器件与存算一体芯片。本次活动由集成电路学院研究员、“齐鲁青年学者”王天宇主讲,学院党委副书记路丽丽主持活动。

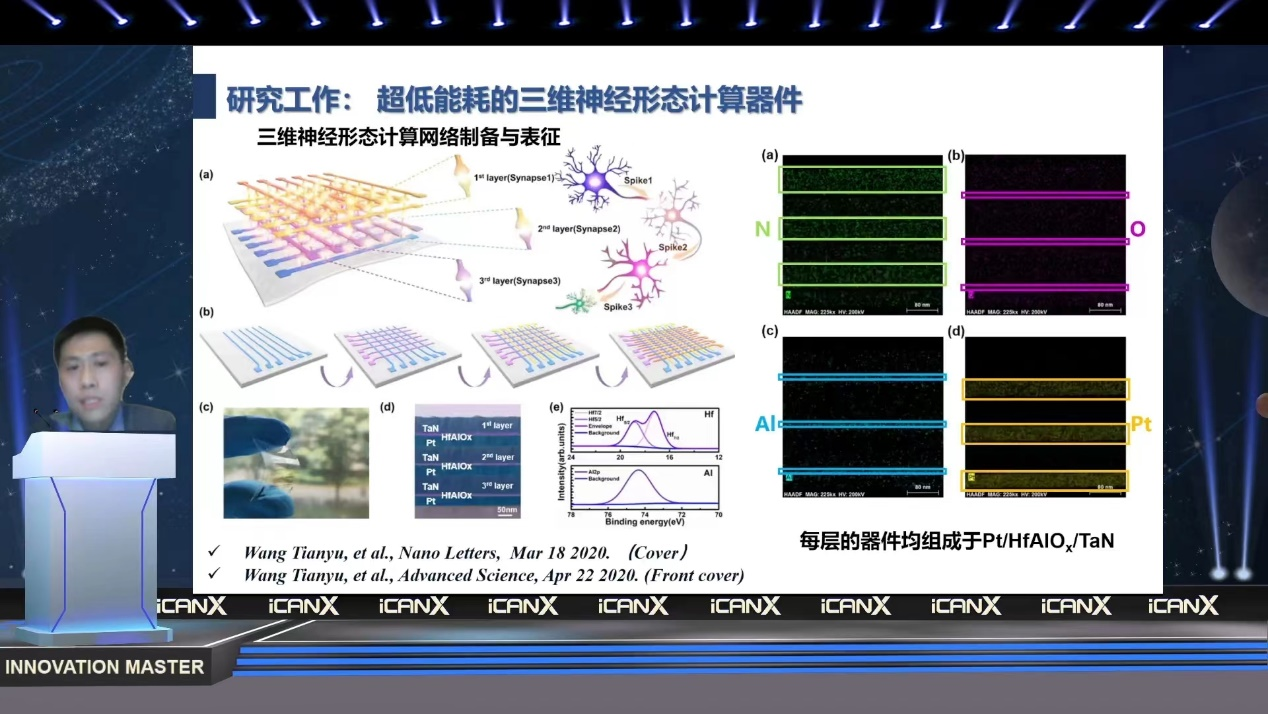

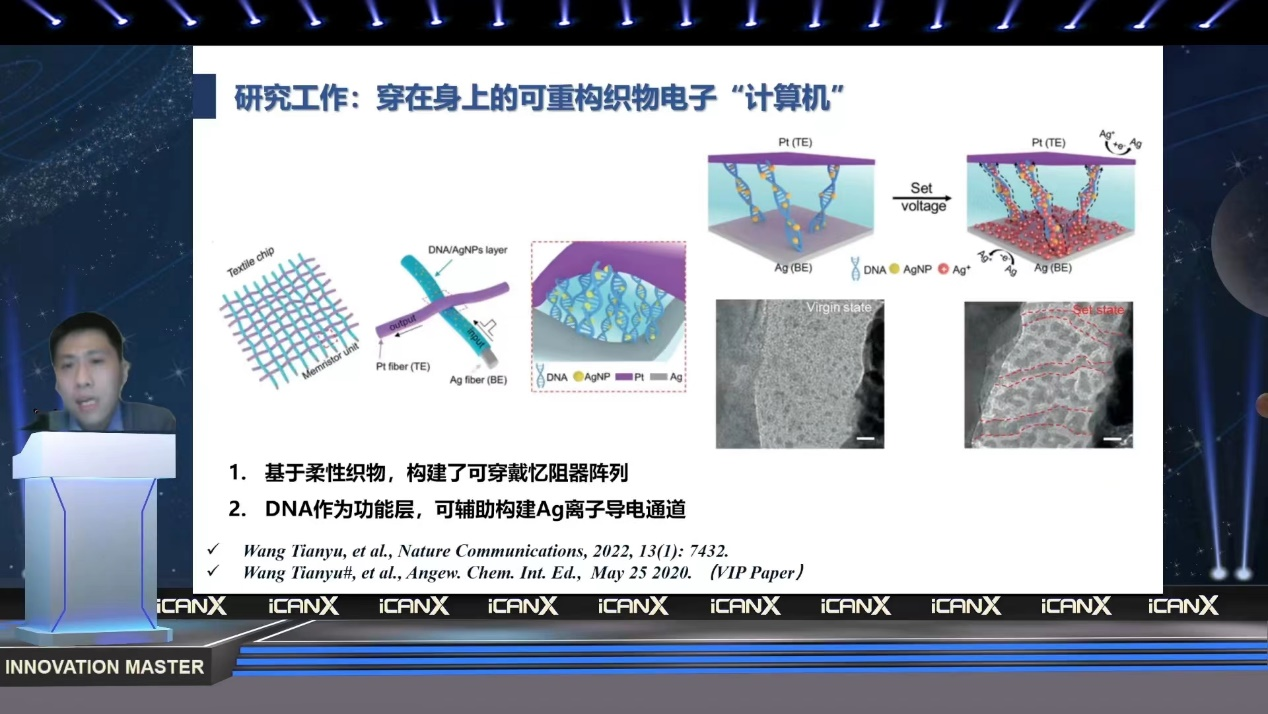

在报告中,王天宇详细介绍了其团队在柔性神经形态类脑器件、低功耗存算一体芯片、铪基铁电隧道结存储器等领域的研究成果。他的团队开发的低功耗神经形态器件在性能指标上已达到国际领先的阿焦耳级(aJ级),这一成就标志着我国在该领域的研究已站在了世界前沿。

随着人工智能技术的不断发展,数据处理需求的日益增长对计算架构提出了更高的要求。王天宇指出,传统的冯·诺依曼架构因存储与计算分离而面临算力不足和高功耗的问题。尽管图形处理单元和三维堆叠存储器等技术已被用来缓解这些问题,但它们无法从根本上解决“存储墙”问题。

为了克服这一挑战,王天宇的团队致力于开发存算一体系统,这种系统能够在存储单元中直接进行计算任务,从而显著提高计算效率。他们受到人脑工作方式的启发,利用电子器件模拟神经网络,通过忆阻器模拟神经突触的权重调节过程,为类脑计算领域带来了新的可能性。

王天宇强调,虽然基于柔性忆阻器的神经形态计算体系在材料、工艺、器件制备、阵列协同和整合集成等方面仍处于发展阶段,但他的团队已经在这些领域取得了显著进展,并将继续深入研究。

王天宇的研究成果不仅在学术界获得了广泛认可,发表了70余篇SCI论文,申请了30余项发明专利,还获得了教育部自然科学二等奖、中国芯片科学年度十大进展等多项荣誉。他的工作为解决当前计算架构的局限性提供了新的视角,并为未来智能计算设备的发展奠定了坚实的基础。

在报告的最后,王天宇展望了存算一体器件与系统的应用前景,他认为这种集成了类脑模拟计算与数字逻辑计算的设备,将能够有效处理多种类型的数据,具有巨大的市场。

本次活动是“芯”系未来系列活动——“芯科研”的第二十三期活动。通过王天宇的讲解,学生们对类脑器件与存算一体芯片有了初步了解,拓宽了学生们的视野,提高了他们对集成电路前沿领域的兴趣。